Day 32: The Art of Interrupt Handling

After spending countless hours debugging a particularly nasty timing issue in one of my embedded projects last week, I thought I’d share my learning of interrupt handling. Trust me, once you understand what’s happening under the hood, you’ll never look at your keyboard the same way again!

Introduction

Think of interrupts like having a really attentive assistant while you’re deeply focused on work. You’re in the zone, cranking out code, when suddenly your phone rings. Without thinking, your brain automatically “interrupts” your coding flow to handle this new input. That’s exactly how computers handle interrupts - they’re those “excuse me, but this is important” moments that need immediate attention.

The Hidden Orchestra of Your Computer

Every time you press a key or move your mouse, there’s an incredible symphony of events happening beneath the surface. Let me break down this fascinating process that I’ve spent years working with.

The Hardware Dance

At the lowest level, when you press a key, a electrical signal travels through your keyboard’s circuitry. This creates what we call an Interrupt Request (IRQ) - essentially a tiny electrical pulse saying “Hey CPU, I need your attention!”

What’s really cool is how the CPU handles these requests. Inside the CPU, there’s a special pin called the INT pin. When an interrupt arrives, this pin gets activated, and the CPU springs into action like a well-trained emergency responder.

The Kernel’s Security Guard

Now, here’s where it gets really interesting. The kernel (the core of the operating system) acts like a strict bouncer at an exclusive club. It maintains what we call an Interrupt Descriptor Table (IDT) - think of it as a VIP guest list for interrupts. Each interrupt gets its own special entry in this table, complete with instructions on how to handle it.

Here’s a peek at what this looks like in x86 architecture (one of my favorite parts of low-level programming):

; Example of an IDT entry structure

struc IDT_ENTRY

.offset_low resw 1 ; Lower 16 bits of handler address

.selector resw 1 ; Kernel segment selector

.zero resb 1 ; Reserved

.type_attr resb 1 ; Type and attributes

.offset_high resw 1 ; Higher 16 bits of handler address

endstruc

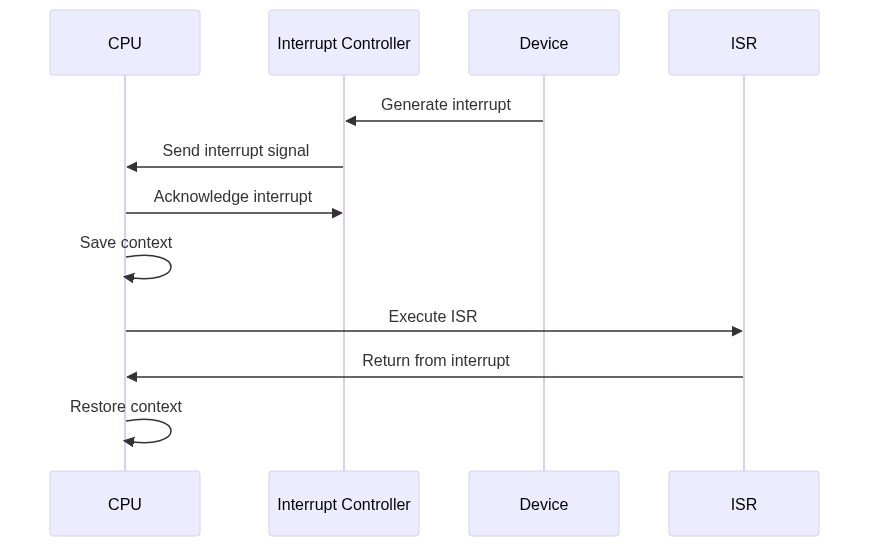

The Context Switch Ballet

When an interrupt occurs, the CPU needs to save everything it was doing - and I mean everything. This process, called a context switch, is like taking a perfect snapshot of the CPU’s state. Let me walk you through what happens:

- The CPU pushes all its current registers onto a stack

- It saves the current program counter (the address of the next instruction)

- It switches to a different privilege level (usually ring 0)

- It loads the address of the interrupt handler

- Finally, it jumps to the handler code

This entire sequence happens in just a few CPU cycles - it’s incredibly fast and precisely choreographed.

The Software Side: Where the Magic Happens

Let me share a real-world example that I often use when teaching this concept. Here’s a more detailed version of an interrupt handler, with some extra features I’ve found useful:

#include <stdio.h>

#include <signal.h>

#include <unistd.h>

#include <time.h>

volatile sig_atomic_t interrupt_count = 0;

time_t last_interrupt_time = 0;

void detailed_interrupt_handler(int sig) {

time_t current_time = time(NULL);

interrupt_count++;

printf("\n=== Interrupt Details ===\n");

printf("Signal received: %d\n", sig);

printf("Interrupt count: %d\n", interrupt_count);

if (last_interrupt_time != 0) {

printf("Time since last interrupt: %ld seconds\n",

current_time - last_interrupt_time);

}

last_interrupt_time = current_time;

}

int main() {

struct sigaction sa;

sa.sa_handler = detailed_interrupt_handler;

sigemptyset(&sa.sa_mask);

sa.sa_flags = SA_RESTART;

if (sigaction(SIGINT, &sa, NULL) == -1) {

perror("Failed to set up interrupt handler");

return 1;

}

printf("Interrupt handler demonstration running...\n");

printf("Press Ctrl+C to trigger an interrupt\n");

while (1) {

sleep(1);

}

return 0;

}

The Kernel’s Perspective

Now, let’s peek behind the curtain and see how the kernel manages all this. I remember being fascinated when I first learned about this part. The kernel maintains several key structures:

The Interrupt Stack Table (IST)

Each CPU core has its own interrupt stack table, which provides dedicated stacks for handling different types of interrupts. This is crucial for preventing stack overflow issues during nested interrupts - something that caused me many headaches early in my career!

Here’s what the kernel’s interrupt stack looks like in memory:

Priority and Nesting

One of the most elegant aspects of interrupt handling is how it manages priority levels. Think of it like a hospital emergency room - critical cases get immediate attention, while less urgent ones wait their turn.

The kernel uses a priority-based system with something called the Task Priority Register (TPR). Higher priority interrupts can interrupt lower priority ones, creating what we call “nested interrupts.” Here’s how it typically works:

- A low-priority interrupt (like a keyboard press) is being handled

- A high-priority interrupt (like a hardware error) comes in

- The CPU pauses the low-priority handler

- Handles the high-priority interrupt

- Resumes the low-priority handler

Real-World Applications and Gotchas

Below you can see some:

The Race Condition Trap

One of the trickiest issues with interrupts is dealing with race conditions. Imagine you’re updating a counter in your main code when an interrupt hits and tries to modify the same counter. This is why we use special variables (like volatile sig_atomic_t in C) and hardware synchronization primitives.

Timing is Everything

Interrupt latency - the time between when an interrupt occurs and when it’s handled - is crucial in real-time systems. I once worked on a project where inconsistent interrupt latency caused subtle timing issues that only showed up under heavy load. The solution? Careful priority management and interrupt masking.

The Hidden Cost

While interrupts are powerful, they come with overhead. Each context switch takes time, and too many interrupts can seriously impact performance. I learned this the hard way when working on a high-performance embedded system where excessive interrupt handling was creating noticeable delays.

Future Directions and Modern Challenges

The world of interrupt handling keeps evolving. Modern processors introduce fascinating new concepts like:

Message Signaled Interrupts (MSI)

Instead of using dedicated interrupt lines, MSI uses memory writes to signal interrupts. This approach is becoming increasingly popular in modern hardware, especially in PCI Express devices.

Interrupt Threads

Modern kernels often handle interrupts in dedicated threads, allowing for better resource management and scheduling. This approach helps prevent priority inversion and makes interrupt handling more predictable.

Closing Thoughts

After spending years working with interrupts at various levels, from bare metal to high-level operating systems, I’m still amazed by their elegance. They’re a perfect example of how hardware and software work together to create the responsive computing experience we take for granted.

Remember, every time you press a key or click your mouse, you’re initiating this incredible dance of hardware signals, kernel management, and software responses. It’s this kind of intricate coordination that makes modern computing possible.

I’d love to hear about your experiences with interrupt handling! Have you ever encountered any particularly challenging interrupt-related bugs? How did you solve them? Let me know in the comments below!

Note: This post is based on my personal experience working with various systems. Different architectures and operating systems might handle interrupts slightly differently, but the core concepts remain the same.